uvm memo

Architecture

Basic entities

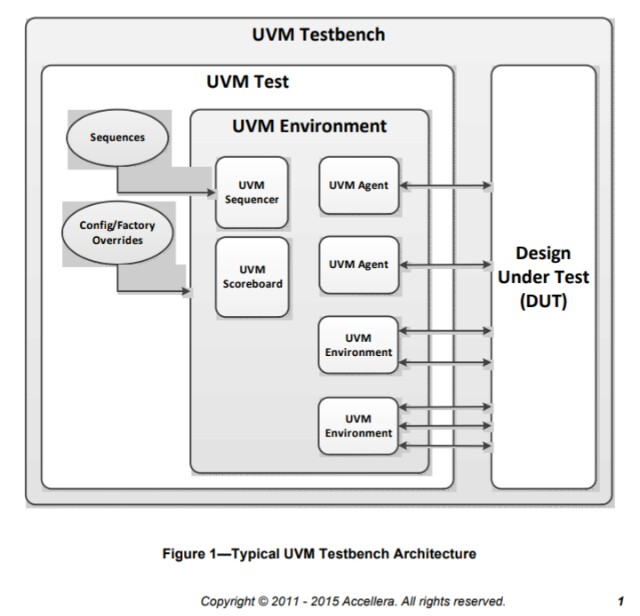

1.1 The Typical UVM Testbench Architecture 1.1.1 UVM Testbench 1.1.2 UVM Test 1.1.3 UVM Environment 1.1.4 UVM Scoreboard 1.1.5 UVM Agent 1.1.6 UVM Sequencer 1.1.7 UVM Sequence 1.1.8 UVM Driver 1.1.9 UVM Monitor 1.2 The UVM Class Library 2. Transaction-Level Modeling (TLM) 3. Developing Reusable Verification Components

Typical Architecture

Class Library

Agent

Agent - Sequencer, Driver, Monitor

テストベンチの階層構造

| Layer | Description | class |

|---|---|---|

| Test Layer | 試験の最上位 | test |

| scenario | トランザクションのシーケンスを生成 | sequence? |

| Function | 高位のコマンドを生成する。例えば、上位からトランザクションを受け取り、下位のコマンドに分解する。 | sequencer? |

| Command | コマンドを信号に変換して信号層に送付する。 | Driver |

| Signal/DUT | 信号を処理する。上位からの信号を処理し、DUTからの信号やアサーションを上位に送る。 | DUT |

Testで複数/単数のシーケンスを選択し、シーケンスをシーケンサーがコマンドに変換し、ドライバーがコマンドを信号に変換し、DUTに信号を伝える。

このフローを纏めると。

test - sequence - sequencer - driver - DUT

Phase

uvm_test のサブクラス等に実装する。

| phase | Description |

|---|---|

| build_phase | 階層トップから呼ばれる |

| connect_phase | 例えばTLM port接続 |

| end_of_elaboration_phase | 接続終了後に呼ばれる。構成表示等ではに使用される |

| start_of_simulation_phase | シミュレーション開始直前に呼ばれる。初期化等 |

| run_phase | 実行 |

| extract_phase | 終了後、結果出力等 |

| check_phase | 結果チェック等 |

| report_phase | レポート等 |

run_phase は、更に分かれる

reset, configure, main, shutdownと、それぞれにpreとpostの合計12phase 。

各フェーズの実装が、taskとfunction voidに分かれていて気持ち悪く感じる面もある。どちらを使っても良いのだろうか?

そもそもfunctionとtaskを分ける必要性について疑義があり、趣味の世界かもしれない。まあ、Verilogでは制約が異なり、ツールの簡素化や人の勘違い防止には役立っているのかも知れないが、見せかけかな。

objection sim開始と終了

class t extends uvm_env; task run_phase(uvm_phase p); p.raise_objection(this); do_something(); p.drop_objection(this); endtask endclass

env, agent

env : agent等のコンテナ。

agent : sequencer, driver, monitor等のコンテナ

ソース

https://www.doulos.com/knowhow/sysverilog/uvm/easier_uvm_guidelines/layering/

おまけ

// Style #1: Only single `ifdef `ifdef <FLAG> // Statements `endif // Style #2: `ifdef with `else part `ifdef <FLAG> // Statements `else // Statements `endif // Style #3: `ifdef with additional ifdefs `ifdef <FLAG1> // Statements `elsif <FLAG2> // Statements `elsif <FLAG3> // Statements `else // Statements `endif

おまけ2

interfaceはverilogになく、SystemVerilog で定義された。何気にverilogでinterfaceを使いたくなる。

uvm component階層

2uvm_top.uvm_test_top

env配下

uvm_top.uvm_test_top.env.scoreboard

uvm_top.uvm_test_top.env.agent

agent配下

uvm_top.uvm_test_top.env.agent.driver

uvm_top.uvm_test_top.env.agent.monitor uvm_top.uvm_test_top.env.agent.sequensor